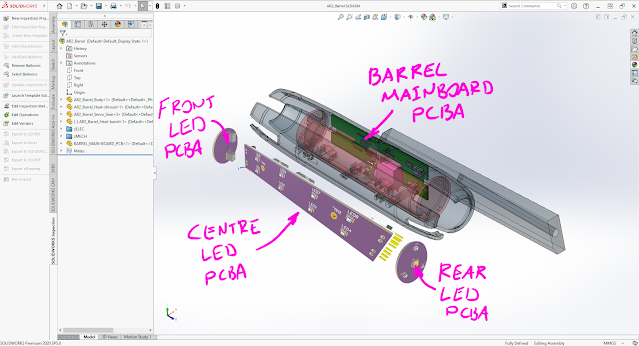

After many late nights and long train rides the AR2 Barrel electronics are complete! For those curious the electronics assembly consists of 4 PCBAs:

BARREL_MAIN-BOARD

- The Big Boss

- Holds various switching & linear regulators that power servo & RED/WHT/RGB LEDs

- LED brightness/colour & servo position are controlled with PCA9685PW, which itself is controlled via I2C

- Lastly, as this is the main gateway to other PCBAs (one of which will be over a long cable...), the board has additional filtering & protection to improve EMI & ESD performance

BARREL_LED-CARRIER-CENTRE

- Holds a pair of RGB LED chains for barrel glow effect

- Interfaces to front & rear PCBAs

- Has some really cool artwork on the silkscreen/overlay ;^)

BARREL_LED-CARRIER-FRONT

- Holds RGB & WHT LEDs for barrel glow & muzzle flash effect

BARREL_LED-CARRIER-REAR

- Holds RGB & RED LEDs for barrel & shell glow effect

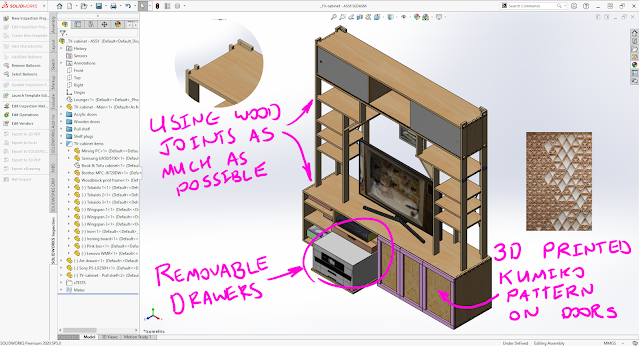

And here's how the AR2 Barrel MECH & ELEC assembly looks like:

Deep-dive into BARREL_MAIN-BOARD PCBA

Just like with the RECEIVER_MAIN-BOARD I want to give a quick rundown of what I am happy with and what I know could be better (you know... have I had more time). But before getting into the nitty gritty here is a cool timelapse of the board being laid out in Altium:

The Good

1. GOOD, Solid 0V reference plane for high energy switching zones

All of my switching regulators and complementary EMI filters are located on the bottom side, away from the "sensitive" digital zones on top layer. ~0.2mm below the bottom layer I have a solid 0V reference plane, ensuring that the high energy current traces have a closely coupled return path (think small current loop area, translating to lower emissions)

And for those tracks that change their reference plane (as in jump from bottom to top layer), I make sure to use a 1N stitching capacitor to assist with the return path. More on this in the BAD section

2. GOOD, Better suited bulk capacitors (package wise)

Previously I was using 0603 sized ceramic capacitors for decoupling, filtering, & general bulk storage. A downside of such a "small" package (depending who you ask) is that with a typical X5R/X7R dielectric the capacitance will be dependant on bias voltage (and temperature), something most manufacturers don't show in their datasheet:

NOTE: Electrolytic & tantalum capacitors also have this behaviour, and from memory polymer versions of the two are not as impacted. But as always you need to check the datasheet to know what to expect... as you can get drastically different performance with same dielectric material

Is this a problem? As always, it depends on the application. But here are a couple of solutions/scenarios if I wanted to stick with using a ceramic capacitors:

- Use a dielectric that is "independent" on bias voltage or package temperature, like C0G/NP0. This is the way to go when precision is required (say an active filter), BUT be wary that getting a C0G capacitor that is >100N is going to get expensive

- Use a physically larger package (1206 instead of 0603) as having more bulk material assists with bias & temperature behaviour, BUT as you can expect this is at the cost of additional board space. Luckily for me I had plenty of that, so I just upped the package size:

3. GOOD, Better suited EMI filter

An improvement to my previous design the EMI filter topology has been changed from pi to T. Which is more appropriate when source & load impedances are LOW (like they are here)

The Bad

1. BAD, Top side tracks have a poor reference plane

I am very happy with my 0V reference plane (bottom side tracks), but I don't have the same enthusiasm for the reference plane used by the top side tracks... as the thing is incredibly choppy:

What does this mean? Well I can expect to see increased emissions, as the return current for each trace can no longer run directly underneath. James Pawson of Unit 3 Compliance has a really good video on this, but below are some key slides to explain the issue:

To help this discontinuity in return path I have sprinkled as many reference plane stitching capacitors as I can across the board. But now that I think of it I should have just poured 0V on the top side and stitched it to the internal 0V reference plane with a matrix of vias, spaced to reflect the highest frequency of concern

2. BAD, LED connector positions could be better

Though I am quite happy with the tight layout on the bottom side, once the LED related nets make their way to the top side the trace lengths become unpleasantly long due to the connector positions. Again I can expect increased emissions due to the larger loop area D:

An easy solution would be to move the connectors (not possible), or throw more layers at the board

3. BAD, EM zone boundary filters could still be better

J101 could easily have a common mode choke on all 3 data lines, as each pin has a 0V conductor next to them...

J102, P100, & P101 do not have a filter at all... So expect worse emissions (EM noise getting out) & susceptibility (EM noise getting in) performance here

Schematic & PCBA

And to close it all off, here are the BARREL_MAIN-BOARD schematics:

And the PCBAs